### FUNCTION OF EACH BLOCK

### (1) Register

The HD44780 has two g-bit registers, an instruction register (IR) and a data register (DR).

The IR stores instruction codes such as display clear and cursor shift, and address information for display data RAM (DD RAM) and character generator RAM (CG RAM). The IR can be written from the MPU but not read by the MPU.

The DR temporarily stores data to be written into the DD RAM or the CG RAM and data to be read out from DD RAM or CG RAM. Data written into the DR from the MRU is automatically written into the DD RAM or the CG RAM by internal operation. The DR is also used for data storage when reading data from the DD RAM or the CG RAM. When address information is written into the IR, data is read into the DR from the DD RAM or the CG RAM by internal operation. Data transfer to the MPU is then completed by the MPU reading DR. After the MPU reads the DR, data in the DD RAM or CG RAM at the next address is sent to the DR for the next read from the MPU. Register selector (RS) signals make their selection from these two registers.

Table 2 Register Selection

| RS  | R/W  | Operation                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-----|------|-----------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| 010 | 0 IR | write as internal operation (Display clear, etc.)         |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0   | 1    | Read busy flag (DB7) and address counter (DB0 $\sim$ DB6) |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 1   | 0    | DR write as internal operation (DR to DD or CG RAM)       |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 1   | 1    | DR read as internal operation (DD or CG RAM to DR)        |  |  |  |  |  |  |  |  |  |  |  |  |  |

(2) Busy flag (BF)

When the busy flag is "1", the HD44780 is in the internal operation mode, and the next instruction will not be accepted. As Table 2 shows, the busy flag is output to DB7 when RS=0 and R/W=1. The next instruction must be written after ensuring that the busy flag is "0".

(3) Address counter (AC)

The address counter (AC) assigns addresses to DD and CG RAMs. When an instruction for address is written in IR, the address information is sent from IR *to* AC. Selection of either DD or CG RAM is also determined concurrently by the instruction.

After writing into (or reading from) DD or CG RAM display data, AC is automatically incremented by +1 (or decremented by -1). AC contents are output to DBO  $\sim DB_6$  when RS=0 and R/W=1, as shown in Table 2.

(4) Display data RAM (DD RAM)

The display data RAM (DD RAM) stores display data represented in 8-bit character codes. Its capacity is 80x8 bits, or 80 characters. The display data RAM (DD RAM) that is not used for display can be used as a general data RAM. Relations between DD RAM addresses and positions on the liquid crystal display are shown below.

The DD RAM address (ADD) is set in the Address Counter (AC) and is represented in hexadecimal.

↓Upper

Order

Lower

Order

Bits

Bits

Bits

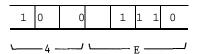

AC

AC6

AC5

AC4

AC3

AC2

AC1

AC0

- Hexadecimal - Hexadecimal -

(Example) DD RAM address "4E"

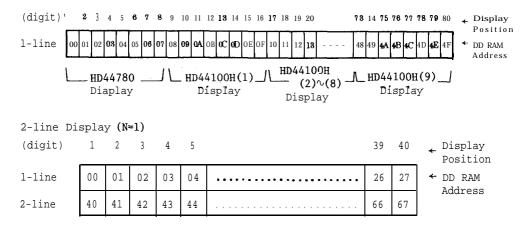

1-line Display (N=O)

| (digit) | 1  | 2  | 3  | 4  | 5  | 79     | 80 | ← Display<br>← Position |

|---------|----|----|----|----|----|--------|----|-------------------------|

| l-line  | 00 | 01 | 02 | 03 | 04 | <br>4E | 4F | ← DD RAM<br>Address     |

(a) When the display characters are less than 80, the display begins at the head position. For example, 8 characters using 1 HD44780 are displayed as:

| (digit) | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | * | Display<br>Position |  |  |

|---------|----|----|----|----|----|----|----|----|---|---------------------|--|--|

| l-line  | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | * | DD RAM<br>Address   |  |  |

When the display shift operation is performed, the DD RAM address moves as:

| HD44780                     |                                                                                                                                                                                                                   |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11044700                    |                                                                                                                                                                                                                   |

| (Left<br>Shift<br>Display)  | 01 02 03 04 05 06 07 08                                                                                                                                                                                           |

| (Right<br>Shift<br>Display) | 4F 00 01 02 03 04 05 06                                                                                                                                                                                           |

| (b)                         | 16-character display using an HD44780 and an HD44100H is as shown below:                                                                                                                                          |

| (digit)                     | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 + Display<br>Position                                                                                                                                                      |

| l-line                      | 00 01 02 03 04 05 06 07 08 09 OA OB OC OD OE OF + DD RAM                                                                                                                                                          |

|                             | HD44780 Display HD44100H Display Address                                                                                                                                                                          |

|                             | When the display shift operation is performed, the DD RAM address moves as:                                                                                                                                       |

| (Left<br>Shift<br>Display   | 01 02 03 04 05 06 07 08 09 OA OB OC OD OE OF 10                                                                                                                                                                   |

| (Right<br>Shift<br>Display) | 4F 00 01 02 03 04 05 06 07 08 09 OA OB OC OD OE                                                                                                                                                                   |

| (c)                         | The relation between display position and DD RAM address when the<br>number of display digits is increased through the use of one<br>HD44780 and two or more HD44100H's can be considered an extension<br>of (b). |

|                             | Since the increase can be 8 digits for each additional HD44100H,<br>up to 80 digits can be displayed by externally connecting 9<br>HD44100H's.                                                                    |

-- HD44780

- - -

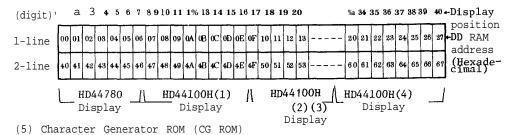

(a) When the number of display characters is less than  $40 \times 2$  lines, the 2 lines from the head are displayed. Note that the first line end address and the second line start address are not consecutive. For example, when an HD44780 is used, 8 characters  $\times$  2 lines are displayed as:

| (digit) | 1  | 2  | 3  | 4  | 5  | б  | 7  | 8  |

|---------|----|----|----|----|----|----|----|----|

| l-line  | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| 2-line  | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

🔔 Display Positio ← DD RAM Address

When display shift is performed, the DD RAM address moves as:

| (Left<br>Shift | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

|----------------|----|----|----|----|----|----|----|----|

| Display)       | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 |

|                |    |    |    |    |    |    |    |    |

| (Right |

|--------|

| Shift  |

| D      |

- Display

| 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

|----|----|----|----|----|----|----|----|

| 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 |

(b) 16 characters  $\times$  2 lines are displayed when an HD44780 and an HD44100H are used.

| (digit) | 1        | 2  | 3    | 4 5 | 56  | 7   | 8   | 9 : | 10 | 11 | 12  | 13  | 31 | 4 3 | 15 | 16 | + | Display<br>Position |

|---------|----------|----|------|-----|-----|-----|-----|-----|----|----|-----|-----|----|-----|----|----|---|---------------------|

| l-line  | 00       | 01 | 02   | 03  | 04  | 05  | 06  | 07  | 08 | 09 | OA  | OB  | OC | OD  | OE | OF | + | DD RAM              |

| 2-line  | 40       | 41 | 42   | 43  | 44  | 45  | 46  | 47  | 48 | 49 | 4A  | 4B  | 4C | 4D  | 4E | 4F |   | Address             |

|         | <u> </u> | HI | )447 | 780 | Dis | pla | у — | /\  |    | HD | 441 | 00н | Di | spl | ay | _  |   |                     |

When display shift is performed, the DD RAM address moves as follows:

| (Left    |   |

|----------|---|

| Shift    |   |

| Display) | ) |

|   |    |    |    |    | 05 |    |    |    |    |    |    |    |    |    |    |    |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| ) | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 |

| (Right<br>Shift   | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | ΟA | OB | OC | OD | OE  |

|-------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| Shiit<br>Display) | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4 E |

(c) The relation between display position and DD RAM address when the number of display digits is increased by using one HD44780 and two or more HD44100H's, can be considered an extension of (b).

Since the increase can be 8 digits  $\times$  2 lines for each additional HD44100H, up to 40 digits 2 lines can be displayed by connecting 4 HD44780's externally.

The character generator ROM generates  $5 \times 7$  dot or  $5 \times 10$  dot character patterns from 8-bit character codes. It can generate 160 types of  $5 \times 7$  dot character patterns and 32 types of  $5 \times 10$  dot character patterns. Table 3 and 4 show the relation between character codes and character patterns in the Hitachi standard HD44780A00 User defined character patterns are also available by mask-programming ROM. For details, see "The LCD-II (HD44780) Breadboard User's Manual".

(6) Character Generator RAM (CG RAM)

The character generator RAM is the RAM with which the user can rewrite character patterns by program. With  $5 \times 7$  dots, 8 byptes of character patterns can be written and with  $5 \times 10$  dots 4 types can be written. Write the character codes in the left columns of Tables 3 and 4 to display character patterns stored in CG RAM.

Table 5 shows the relation between CG RAM addresses and data and display patterns.

As Table 5 shows, an area that is not used for display can be used as a general data RAM.

## Table 3 Correspondence between Character Codes and Character Pattern(Hitachi Standard HD44780A00)

| Higher             |                  | <b></b>   |                | r           | T               | 1                 | T                                      |                      |            |                                                                                        | r              | r          | <b></b>  |

|--------------------|------------------|-----------|----------------|-------------|-----------------|-------------------|----------------------------------------|----------------------|------------|----------------------------------------------------------------------------------------|----------------|------------|----------|

| Lower 4bit<br>4bit | 0000             | 0010      | 0011           | 0100        | 0101            | 0110              | 0111                                   | 1010                 | 1011       | 1100                                                                                   | 1101           | 1116       | 1111     |

| ××××0000           | CG<br>RAM<br>(1) |           | ŀ-'i           | 1           | , <b>I.,, '</b> | ,<br>11           | <b></b>                                |                      | ·····      |                                                                                        | :::            | <u>::</u>  | p        |

| ××××0001           | (2)              | 1         |                | ]]          |                 |                   | -:j                                    | <b>i</b> ;i          | 1.1        | <b>.</b>                                                                               | i,             | ••••       |          |

| ××××0010           | (3)              |           | ·              |             | ŀŗ.             | <u> -</u> ]       | <b> .".</b>                            | 1                    | •1         | ij                                                                                     | ::'            | ·····      | Ö        |

| ××××0011           | (4)              |           |                | ,, .        | :               | ; <mark></mark> . |                                        |                      | ŗj         | 888<br>888<br>88<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | *****<br>***** | :          | <u>.</u> |

| ××××0100           | (5)              | ·••••     | ŗ.             |             |                 |                   | <b>†</b>                               | •.                   |            | ŀ.                                                                                     |                | <b> </b> 4 | <u>.</u> |

| ××××0101           | (6)              | ".<br>• " |                |             |                 | j                 | <b>!</b> !                             |                      | <b>!</b>   |                                                                                        | 1              |            | <br>[[   |

| ××××0110           | (7)              | Ċ.        | <br>           | <br>        | <b>!_!</b>      |                   | I.,I                                   | *****<br>*****<br>** | <b>]</b> ] | ****                                                                                   |                | p          |          |

| ××××0111           | (8)              | :         | ľ              |             |                 |                   | <b>!.!</b>                             |                      |            | ,                                                                                      |                | ;<br>;     | Л        |

| xxxx1000           | (1)              | ľ         |                |             | ×               | ŀ"                |                                        |                      |            |                                                                                        | Ņ              | . <b>ſ</b> |          |

| ××××1001           | (2)              |           | ·              | Ï           |                 | 1                 | ']                                     | <b>11</b> 1          | • <b>*</b> |                                                                                        |                |            |          |

| ××××1010           | (3)              | :#:       | 11<br>11       |             |                 | . 1               | •••••••••••••••••••••••••••••••••••••• |                      | *****      |                                                                                        | <b>]</b> .•    |            | 8        |

| ××××1011           | (4)              |           | #<br>]         |             | <b>.</b>        | k                 | ÷                                      | <b></b>              | <b>†</b>   |                                                                                        |                | <u></u>    |          |

| ××××1100           | (5)              | ;         |                |             |                 | 999               |                                        | 17                   |            | ۱۹۹۹<br>۲<br>۲<br>۳                                                                    | <b>[</b> ]     | \$.        | рц       |

| ××××1101           | (6)              | *****     | 88335<br>79444 | <b>[</b> •] |                 | ויין              |                                        |                      | ••••<br>•• | ·•••                                                                                   | ••,<br>        | <b>:</b>   |          |

| ××××1110           | (7)              | 11        |                | <b>ŀ.</b> ] | ••••            | <b>t"ı</b>        | <b>j</b> .                             |                      | 1 a 1      | •• <b>•</b> ••<br>• <b>•</b> •                                                         | •••            | <u> </u>   |          |

| ××××1111           | (8)              | •••       |                |             |                 | <b>I</b> I        | - <b>!</b>                             |                      | ·          | ••••                                                                                   | []             | <u> </u>   |          |

\*The user can specify any pattern for character-generator KOM.

# Table 4 Relation between CG RAM Addresses and Character Codes (DD RAM) and Character Patterns (CG RAM Data)

| a) For 5 × 1 dot charac                                     | t.er patterns                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Character Codes                                             |                                                                                                                                                                                                                                              | cter Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (DD RAM Data)                                               |                                                                                                                                                                                                                                              | RAM Data)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7 6 5 4 8 2 1 0<br>Higher Lower<br>Order Order<br>Birs Bits | 5 4 8 2 1 0 7 6<br>Higher Lower Highe<br>Order Order<br>Bits Bits Bits                                                                                                                                                                       | 5 4 8 2 1 0<br>r Lower<br>Order_<br>Bits_                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 0 0 0 * 0 0 0                                             | 0 0 0 0 * * * * * * * * * * * * * * * *                                                                                                                                                                                                      | 1       0       0       1         1       0       0       1         1       1       1       0         1       1       1       0         1       0       1       0         1       0       0       0         1       0       0       0         1       0       0       0         1       0       0       0         1       0       0       0         1       0       0       0         1       0       0       0         1       0       0       0 |

| 0 0 0 0 * 0 0 1                                             | 10       0       1       * * 1         0       0       1       1         0       0       1       1         0       0       1       1         1       0       0       1         1       1       0       1         1       1       0       * * | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 0 0 0 * 1 1 1                                             | 0 0 0<br>0 0 1<br>1 1 1<br>1 0 cl<br>1 0 1<br>1 1 1<br>+ *                                                                                                                                                                                   | *No effect                                                                                                                                                                                                                                                                                                                                                                                                                                        |

(a) For 5 × 7 dot charact.er patterns

- (Note) 1: Character code bits 0 2 correspond to CG RAM address bits 3 ~ 5

(3 bits: 8 types).

- 2: CG RAM address bits 0  $\sim$  2 designate character pattern line position. The 8th line is the cursor position and display is performed in logical OR by the cursor.

Maintain the 8th line data, corresponding to the cursor display position, in the "O" state for cursor display. When the 8th line data is "1", bit 1 lights up regardless of cursor existence.

- 3: Character pattern row positions correspond to CG RAM data bits  $0 \sim 4$ , as shown in the figure (bit 4 being at the left end). Since CG RAM data bits  $5 \sim 7$  are not used for display, they can be used for the general data RAM.

- 4: As shown in Table 3 and 4, CG RAM character patterns are selected when character code bits 4  $\sim$  7 are all "0". However, since character code bit 3 is a ineffective bit, the "R" display in the character pattern example, is selected by character code "00" (hexadecimal) or "08" (hexadecimal).

- 5: "1" for CG RAM data corresponds to selection for display and "0" for non-selection.

(b) For  $\times 10$  dot character patterns

| Character Codes                                             | CG RAM                                                                                                                                                                   | Character Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| (DD RAM Data)                                               | Address                                                                                                                                                                  | (CG RAM Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |

| 1 6 5 4 8 2 1 0<br>Higher Lower<br>Order Order<br>Bits Bits | 5 4 3 2 1 0<br>Higher Lower<br>Order Order<br>Bits Bits                                                                                                                  | 7 6 5 4 8 2 1 0<br>Higher Lower<br>Order Order<br>Bits Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 000*00*                                                     | 0 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 11<br>0 0 0 1<br>0 0 0 1<br>0 0 0 1<br>0 0 0 1<br>0 1 0 1<br>0 0 1 0<br>1 0 1<br>1 0 10<br>1 0 1<br>1 1 0 1<br>1 1 1 0<br>1 1 1 1 | *     *     *     0     0     0     0     0       1     0     1     1     0     1       1     1     0     0     1       1     1     0     0     1       1     1     0     0     1       1     1     1     1     1       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     0     0     0       1     1     0     0       1     0     0     0       1     1     0     0       1     1     0     0       1     1     1     1       1     0     0       1     1 <th>Character<br/>Pattern<br/>Example<br/>Cursor<br/>← Position</th> | Character<br>Pattern<br>Example<br>Cursor<br>← Position |

|                                                             |                                                                                                                                                                          | ***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |

|                                                             | 1 1 0 0<br>1 1 0 1<br>1 1 1 0<br>1 1 1 1                                                                                                                                 | * * * * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | *No Effect                                              |

(Note) 1: Character code bits 1, 2 correspond to CG RAM address bits 4, 5

(2 bits: 4 types).

2: CG RAM address bits 0  $\sim$  3 designate character pattern line position. The 11th line is the cursor position and display is performed in logical OR with cursor.

Maintain the 11th line data corresponding to the cursor display position in the "0" state for cursor display. When the 11th line data is "1", bit 1 lights up regardless of cursor existence. Since the 12th ~ 16th lines are not used for display, they can be used for the general data RAM.

- 3: Character pattern row positions are the same as 5  $\times$  7 dot character pattern positions.

- 4: CG RAM character patterns are selected when character code bits 4 7 are all "0". However, since character code bit 0 and 3 are ineffective bits, "P" display in the character pattern example is selected by character code "00", "01", "08" and "09" (hexadecimal).

- 5: "1" for CG RAM data corresponds to selection for display and "0" for non-selection.

#### HD44780 -

(7) Timing Generation Circuit

The timing generation circuit generates timing signals to operate internal circuits such as DD RAM, CG ROM and CG RAM. RAM read timing needed for display and internal operation timing by MPU access are separately **gen**-e.rated so they do not interfere with each other. Therefore, when writing data to the DD RAM, for example, there will be no undersirable influence, such as flickering, in areas other than the display area. This circuit also generates timing signals to operate the externally connected driver LSI HD44100H.

(8) Liquid Crystal Display Driver Circuit

The liquid crystal display driver circuit consists of 16 common signal drivers and 40 segment signal drivers. When character font and number of lines are selected by a program, the required common signal drivers automatically output drive waveforms, the other common signal drivers continue to output non-selection waveforms.

The segment signal driver has essentially the same configuration as the driver LSI HD44100H. Character pattern data is sent serially through a 40-bit shift register and latched when all needed data has arrived. The latched data controls the driver for generating drive waveform outputs. The serial data is sent to the HD44100H, externally connected in cascade, used for display digit number extension.

Send of serial data always starts at the display data character pattern corresponding to the last address of the display data RAM (DD RAM). Since serial data is latched when the display data character pattern, corresponding to the starting address, enters the internal shift register, the HD44780 drives the head display. The rest displays, corresponding to latter addresses, are added with each additional HD44100H.

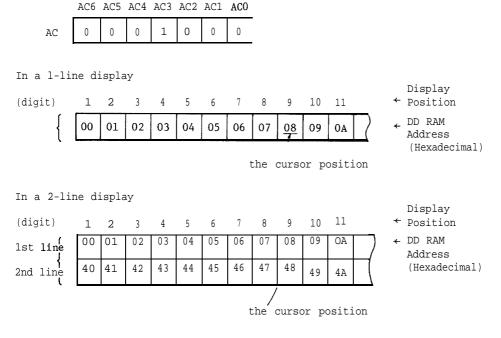

(9) Cursor/Blink Control Circuit

This is the circuit that generates the cursor or blink. The cursor or the blink appear in the digit residing at the display data RAM (DD RAM) address set in the address counter (AC).

When the address counter is  $(08)_{16}$ , a cursor position is:

(Note) The cursor or blink appears when the address counter (AC) selects the character generator RAM (CG RAM). But the cursor and blink are meaningless.

The cursor or blink is displayed in the meaningless position when AC is the CG RAM address.