#### **@ELECTRICAL CHARACTERISTICS**

#### • Absolute Maximum Ratings

| Item                     | Symbol          | Limit                           | Unit | Note |

|--------------------------|-----------------|---------------------------------|------|------|

| Power Supply Voltage (1) | V <sub>CC</sub> | -0.3 to +7.0                    | v    |      |

| Power Supply Voltage (2) | V1 to V5        | $V_{CC}$ -13.5 to $V_{CC}$ +0.3 | v    | 3    |

| Input Voltage            | ٧ <sub>T</sub>  | -0.3 to V <sub>CC</sub> +0.3    | v    |      |

| Operating Temperature    | Topr            | -20 to +75                      | °C   |      |

| Storage Temperature      | Tstg            | -55 to +125                     | °C   |      |

- Note 1: If LSI's are used above-absolute maximum ratings, they may be permanently destroyed. Using them within electrical characteristic limits is strongly recommended for normal operation. Use beyond these conditions will cause malfunction and poor reliability.

- Note 2: All voltage values are referenced to GND=OV.

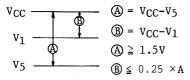

- Note 3: Applies to V1 to V5. Must maintain  $V_{CC} \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$ (high  $\leftarrow \rightarrow low$ )

# • Electrical Characteristics (VCC = $5V\pm10\%$ , Ta = -20 to $+75^{\circ}$ C)

| <u>.</u>                         |                                                                                                       | Test                                                                         | <del>,</del> T       | Limit   |                   |            |             |

|----------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|---------|-------------------|------------|-------------|

| Item                             | Symbol                                                                                                | condition                                                                    | min                  | typ max |                   | Unit       | Note        |

| Input "High" Voltage (1)         | V <sub>IH1</sub>                                                                                      |                                                                              | 2.2                  | -       | ¥сс               | v          | (2)         |

| Input "Low" Voltage (1)          | V <sub>TT 1</sub>                                                                                     |                                                                              |                      | -       | 0.6               | ¥          | (2)         |

| output "High" voltage(1) (TTL)   | VOH1                                                                                                  | -1 <sub>OH</sub> =0.205mA                                                    | 2.4                  | -       | -                 | v          | (3)         |

| Output "Low" Voltage (1) (TTL)   | VOLI                                                                                                  | IOL=1.2mA                                                                    |                      | -       | 0.4               | V          | (3)         |

| Output "High" Voltage (2)(CMOS)  | V <sub>OH2</sub>                                                                                      | -1 <sub>OH</sub> =0.04mA                                                     | 0.'9V <sub>CC</sub>  | -       |                   | v          | (4)         |

| Output "Low" Voltage (2) (CMOS)  | V <sub>OL2</sub>                                                                                      | LOL=0.04mA                                                                   |                      | -       | 0.1V <sub>C</sub> | ç v        | (4)         |

| Driver Voltage Descending (COM)  | VCOM                                                                                                  | Id=0.05mA                                                                    |                      | -       | 2.9               | v          | (10)        |

| Driver Voltage Descending (SEG)  | VSEG                                                                                                  | Id=0.05mA                                                                    |                      | -       | 3.8               | v          | (10)        |

| Input Leakage Current            | IIL                                                                                                   | Vin=0 to V <sub>CC</sub>                                                     | -1                   | ł       | 1                 | μA         | (5)         |

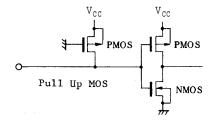

| Pull UP MOS Current              | -1 <sub>P</sub>                                                                                       | Vrr=5V                                                                       | 50                   | 125     | 250               | μA         |             |

| Power Supply Current (1)         | Ceramic filter<br>I <sub>CC1</sub>   oscillation<br>V <sub>CC</sub> =5V, f <sub>OSC</sub> =<br>250kHz |                                                                              |                      | 0.55    | 0. 8              | _ m.4.<br> | (6)         |

| Power Supply Current (2)         | I <sub>CC2</sub>                                                                                      | Rf oscillation<br>External clock<br>operation<br>Vcc=5V, fosc=<br>fcp=270kHz |                      | 0.35    | 0.6               | mA<br>-    | (6)<br>(11) |

| External Clock Operation         |                                                                                                       | -                                                                            | <b>.</b>             |         |                   |            |             |

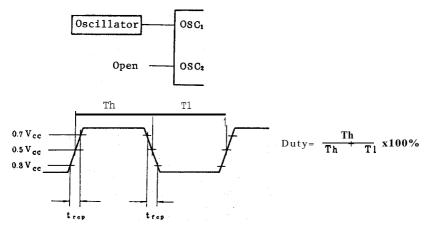

| External Clock Frequency         | f <sub>cp</sub>                                                                                       | ******                                                                       | 125                  | 250     | 350               | kHz        | (7)         |

| External Clock Duty              | Duty                                                                                                  |                                                                              | 45                   | 50      | 55                | %          | (7)         |

| External Clock Rise Time         | t <sub>rcp</sub>                                                                                      |                                                                              |                      |         | 0.2               | us         | (7)         |

| External Clock Fall Time         | tfcp                                                                                                  |                                                                              |                      |         | 0.2               | μs         | (7)         |

| Input "High" Voltage (2)         | V <sub>IH2</sub>                                                                                      |                                                                              | V <sub>CC</sub> -1.0 | ł       | Vcc               | v          | (12)        |

| Input "Low" Voltage (2)          | V <sub>IL2</sub>                                                                                      |                                                                              | -0.3                 | -       | 1.0               | v          | (12)        |

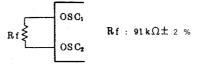

| Internal Clock Operation (Rf osc | illation                                                                                              | )                                                                            |                      |         |                   |            |             |

| Clock Oscillation Frequency      | fosc                                                                                                  | $Rf = 91k\Omega \pm 2\%$                                                     | 190                  | 270     | 350               | kHz        | (8)         |

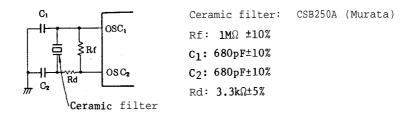

| Internal Clock Operation (Cerami | c filter                                                                                              | oscillation)                                                                 |                      |         |                   |            |             |

| Clock Oscillation Frequency      | fosc                                                                                                  | Ceramic filter                                                               | 245                  | 250     | 255               | kHz        | (9)         |

| LCD Voltage                      | V <sub>LCD1</sub>                                                                                     | VCC-V5 1/5 bias                                                              | 4.6                  | ~       | 11                | v          | , (13)      |

|                                  | V <sub>LCD2</sub>                                                                                     | 1/4 bias                                                                     | 3.0                  | -       | 11                | v          | (13)        |

#### HD44780

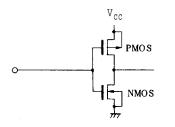

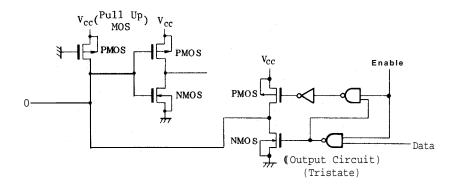

- Note 1: The following are I/O terminal configurations except for liquid crystal display output.

- Input Terminal

Applicable Terminals: E

(No pull up MOS)

Applicable Terminals: RS, R/W (With pull up MOS)

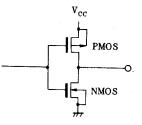

• Output Terminal

Applicable Terminals: CL<sub>1</sub>, CL<sub>2</sub>, M, D

.I/O Terminal

Applicable Terminals: DBO to DB7

Note 2: Input terminals and I/O terminals. Excludes  $OSC_1$  terminals. Note 3: I/O terminals.

Note 4: Output terminals.

- HD44780

- Note 5: Current flowing through pull-up MOS's and output drive MOS's is excluded.

- Note 6: Input/Output current is excluded. When input is at the intermediate level with CMOS, excessive current flows through the input circuit to the power supply. To avoid this, input level must be fixed at high or low.

- Note 7: External clock operation.

Since oscillation frequency varies depending on  $0SC_1\ \text{and}\ 0SC2$  terminal capacity, wiring length for these terminals should be minimized.

Note 9: Internal oscillator operation using a ceramic filter.is used.

HD44780

Note 10: Applies to both  $V_{COM}$  and VSEG voltage drops.

- $v_{COM} \colon$  From poer supply terminal VCC, Vl, V4, V5 to each common signal terminal (COM1 to COM16)

- $v_{SEG}$ : From power supply terminal VCC,  $v_2,\,v_3,\,v_5$  to each segment signal terminal (SEG\_1 to SEG\_40)

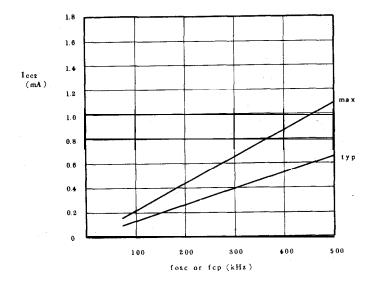

- Note 11: Relation between operation frequency and current consumption is shown in this diagram. ( $V_{CC} = 5V$ )

Note 12: Applied to OSC1 terminal.

Note 13 The condition for COM pin voltage drop (V\_{COM}) and SEG pin voltage drop (V\_{SEG}).

## • Timing Characteristics

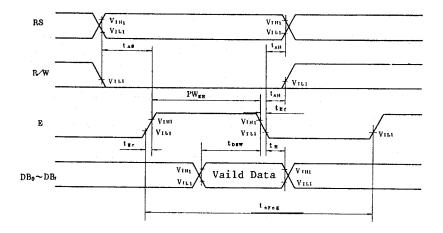

Write Operation

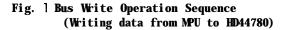

Read Operation

Fig. 2 Bus Read Operation Sequence (Reading out data from HD44780 to MPU)

HD44780

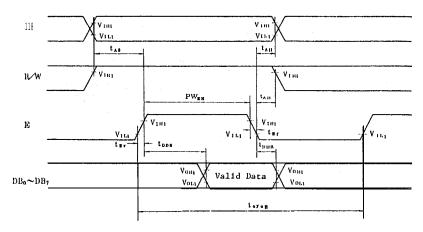

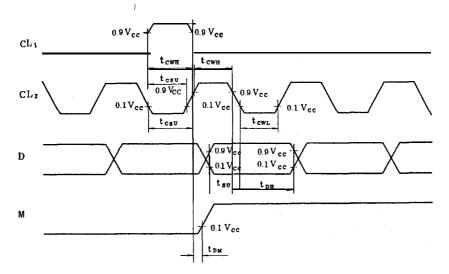

Interface Signal with Driver LSI HD44100H

Fig. 3 Sending Data to Driver LSI HD44100H

## - HD44780

# • BUS Timing Characteristics ( $V_{CC} = 5.0V \pm 10\%$ , GND =0V, Ta =-20 to +75°C)

1

| Item                               | Symbol                            | Test condition | Lim<br>min | it<br>max | Unit |

|------------------------------------|-----------------------------------|----------------|------------|-----------|------|

| Enable Cycle Time                  | t <sub>cyc</sub> E                | Fig. 1         | 1000       | -         | ns   |

| Enable Pulse Width "High"<br>level | PW <sub>EH</sub>                  | Fig. 1         | 450        | -         | ns   |

| Enable Rise/Fall Time              | t <sub>Er</sub> , t <sub>Ef</sub> | Fig. 1         | -          | 25        | ns   |

| Address Set-up Time RS, R/W        | t <sub>AS</sub>                   | Fig. 1         | 140        | -         | ns   |

| Address Hold Time                  | t <sub>AH</sub>                   | Fig. 1         | 10         | 1         | ns   |

| Data Set-up Time                   | <sup>t</sup> DSW                  | Fig. 1         | 195        | -         | ns   |

| Data Hold Time                     | t <sub>H</sub>                    | Fig. 1         | 10         | -         | ns   |

Write Operation (Writing data from MPU to HD44780)

Read Operation (Reading data from HD44780 to MPU)

| Item                  |                 | Symbol                            | Test condition | Limit |               | Unit |

|-----------------------|-----------------|-----------------------------------|----------------|-------|---------------|------|

|                       |                 |                                   | Test condition | min   | max           | UNIL |

| Enable Cycle Time     | · .             | t <sub>cycE</sub>                 | Fig. 2         | 1000  | -             | ns   |

| Enable Pulse Width    | "High"<br>level | pw <sub>eh</sub>                  | Fig. 2         | 450   | s. <u>-</u> . | ns   |

| Enable Rise/Fall Time |                 | t <sub>Er</sub> , T <sub>Ef</sub> | Fig. 2         | -     | 25            | ns   |

| Address Set-up Time   | RS, R/W<br>—E   | t <sub>AS</sub>                   | Fig. 2         | 140   | -             | ns   |

| Address Hold Time     |                 | t <sub>AH</sub>                   | Fig. 2         | 10    | -             | ns   |

| Data Delay Time       |                 | t <sub>DDR</sub>                  | Fig. 2         | -     | 320           | ns   |

| Data Hold Time        |                 | t <sub>DHR</sub>                  | Fig. 2         | 20    | -             | ns   |

HD44780-

# • Interface Signal with HD44100H Timing Characteristics ( $V_{CC} = 5.0V \pm 10\%$ , GND = 0V, Ta =-20 to +75°C)

| Item              |                 | Symbol           | Test condition . | Limit |      | -Unit   |

|-------------------|-----------------|------------------|------------------|-------|------|---------|

|                   |                 |                  |                  | min   | max  | - UIILC |

| Clock Pulse Width | "High"<br>level | tCWH             | Fig. 3           | 800   | -    | ns      |

| Clock Pulse Width | "High"<br>level | t <sub>CWL</sub> | Fig. 3           | 800   | ł    | ns      |

| Clock Set-up Time |                 | t <sub>CSU</sub> | Fig. 3           | 500   | 4    | ns      |

| Data Set-up Time  |                 | t <sub>SU</sub>  | Fig. 3           | 300   | -    | ns      |

| Data Hold Time    |                 | t <sub>DH</sub>  | Fig. 3           | 300   | 1    | ns      |

| M Delay Time      |                 | t <sub>DM</sub>  | Fig. 3           | -1000 | 1000 | ns      |

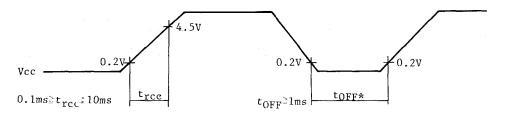

## • Power Supply Conditions Using Internal Reset Circuit

| Item                   | Symbol           | Test condition | Limit |     | Unit |

|------------------------|------------------|----------------|-------|-----|------|

| Item                   | SYNDOT           | Test condition | min   | max | OHIC |

| Power Supply Rise Time | trcc             |                | 0.1   | 10  | ns   |

| Power Supply OFF Time  | t <sub>OFF</sub> |                | 1     | -   | ns   |

Since the internal reset circuit will not operate normally unless the preceding conditions are met, initialize by instruction. (Refer to "Initializing by Instruction")

(Note)  $t_{\rm OFF}$  stipulates the time of power OFF for power supply instantaneous dip or when power supply repeats ON and OFF.